MIPS architecture

De LibreFind

| Advanced search |

- About 12 results found and you can help!

MIPS (originally an acronym for Microprocessor without Interlocked Pipeline Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by MIPS Technologies (formerly MIPS Computer Systems, Inc.). The early MIPS architectures were 32-bit, and later versions were 64-bit. Multiple revisions of the MIPS instruction set exist, including MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS32, and MIPS64. The current revisions are MIPS32 (for 32-bit implementations) and MIPS64 (for 64-bit implementations). MIPS32 and MIPS64 define a control register set as well as the instruction set.

| MIPS Technologies MIPS Technologies mips.com - Web |

| MIPS Technologies Developers MIPS Technologies Developers developer.mips.com - Web |

| MIPS Architectures MIPS Architectures www.mips.com/products/architectures/ - Web |

Gallery for «MIPS architecture»

Average relevance

| Patterson & Hennessy - Appendix A Patterson & Hennessy - Appendix A www.cs.wisc.edu/~larus/HP_AppA.pdf - Web |

| Summary of MIPS assembly language Summary of MIPS assembly language logos.cs.uic.edu/366/notes/MIPS%20Quick%20Tutorial.htm - Web |

| MIPS Instruction reference MIPS Instruction reference www.mrc.uidaho.edu/mrc/people/jff/digital/MIPSir.html - Web |

| MARS (MIPS Assembler and Runtime Simulator) MARS (MIPS Assembler and Runtime Simulator) courses.missouristate.edu/KenVollmar/MARS/ - Web |

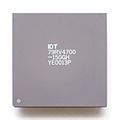

| MIPS processor images and descriptions at cpu-coll... MIPS processor images and descriptions at cpu-collection.de www.cpu-collection.de/?tn=1&l0=cl&l1=MIPS%20Rx000 - Web |

| A programmed introduction to MIPS assembly A programmed introduction to MIPS assembly chortle.ccsu.edu/AssemblyTutorial/ - Web |

| Mips bitshift operators Mips bitshift operators www.cs.umd.edu/.../bitshift.html - Web |

| MIPS software user's manual MIPS software user's manual www.it.uu.se/.../4KcProgMan.pdf - Web |

Low relevance

| MIPS Architecture history diagram MIPS Architecture history diagram meld.org/library/education/mips-architectures - Web |